AMD ha patentado un procesador que cuenta con un acelerador de aprendizaje automático (ML) que se apila sobre un troquel de entrada/salida (IOD). La patente indica que AMD puede planear construir un sistema patentado o un centro de datos en chips (SoC) con aceleradores de aprendizaje automático FPGA o GPU incorporados.

Así como AMD ahora puede agregar caché a sus CPU, puede agregar una FPGA o GPU encima de su plantilla de E/S de procesador. Pero lo que es más importante, la tecnología permite a la empresa agregar otros tipos de aceleradores a los futuros SoC de CPU. Al igual que con cualquier trabajo patentado, una patente no garantiza que veremos diseños con la tecnología lanzada al mercado. Sin embargo, nos da una idea de la dirección que está tomando la empresa en I+D, y existe la posibilidad de que veamos productos basados en esta tecnología, o derivados cercanos, que se lancen al mercado.

Apile un acelerador de IA/ML sobre una plantilla de E/S

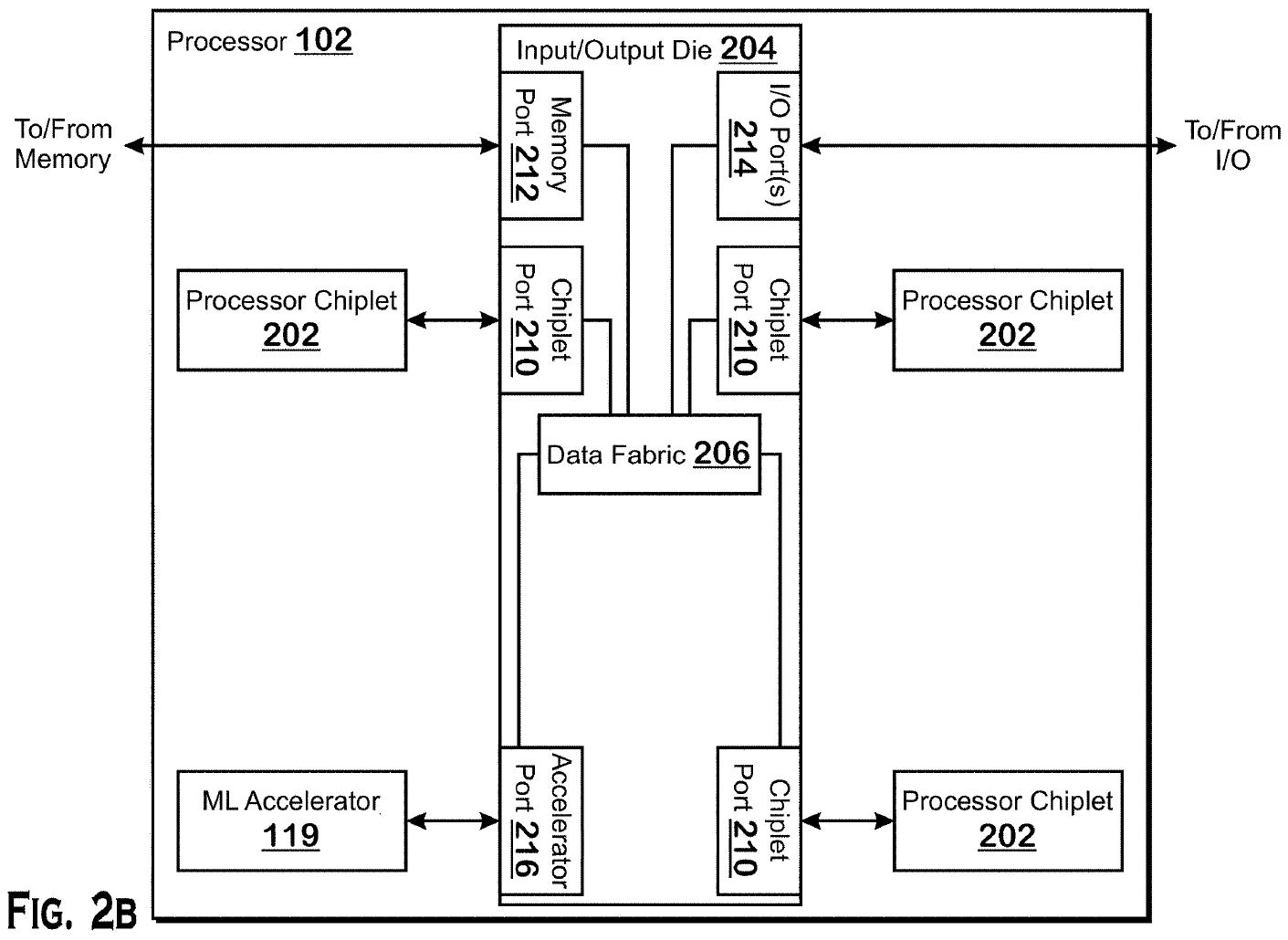

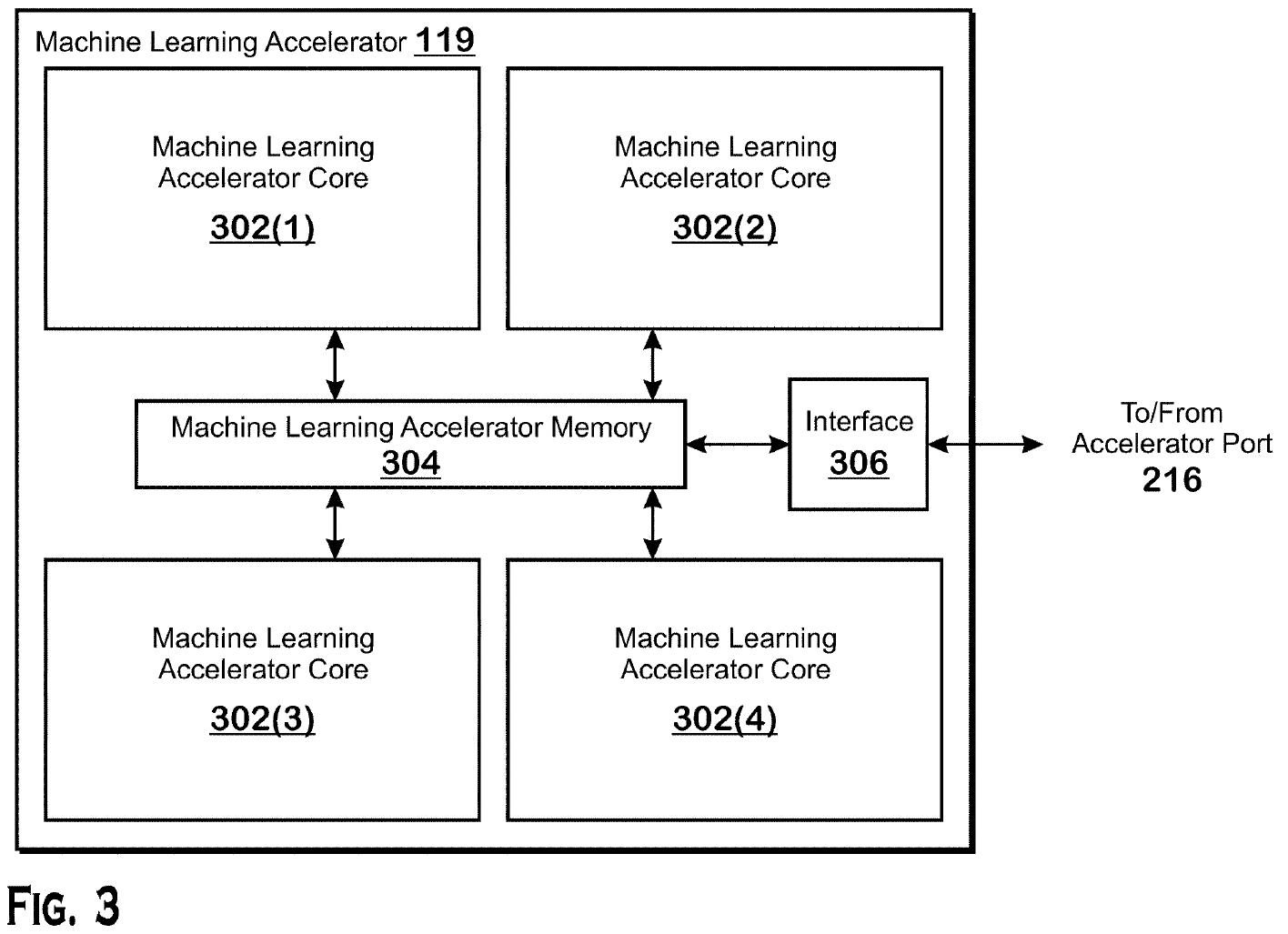

Patente AMD «Acelerador de aprendizaje automático conectado en vivo» Describe explícitamente cómo AMD podría agregar un acelerador ML a sus CPU con IOD utilizando sus tecnologías de apilamiento patentadas. Aparentemente, la tecnología de AMD le permite agregar un Grupo de procesamiento programable (FPGA) o GPU para calcular cargas de trabajo de aprendizaje automático sobre la plantilla de E/S con un puerto de aceleración especial.

AMD describe varias formas de agregar un acelerador: una incluye un acelerador con su propia memoria local, otra indica que dicho acelerador usa memoria conectada al IOD, mientras que en el tercer escenario, el acelerador puede usar la memoria del sistema, y en este es no es necesario apilarlo encima del IOD.

Las tecnologías de aprendizaje automático serán ampliamente utilizadas por los futuros centros de datos. Sin embargo, para ser más competitivo, AMD necesita acelerar las cargas de trabajo de ML con sus chips. Apilar un acelerador de aprendizaje automático sobre un bloque de E/S de CPU permite acelerar significativamente las cargas de trabajo de ML sin incorporar silicio optimizado para ML en los chips de CPU. También ofrece las ventajas de densidad, potencia y transferencia de datos.

La patente se presentó el 25 de septiembre de 2020, poco más de un mes antes de que AMD y Xilinx anunciaran que sus equipos de gestión habían llegado a un acuerdo definitivo en virtud del cual AMD adquiriría Xilinx. La patente se publicó el 31 de marzo de 2022 con el colega de AMD Maxim F. Kazakov figura como inventor. Los primeros productos de AMD con IP de Xilinx se esperan para 2023.

No sabemos si AMD usará su patente para productos reales, pero la elegancia de agregar capacidades de ML a casi cualquier CPU hace que la idea suene plausible. Suponiendo que los procesadores EPYC con nombre en código ‘Genoa’ y ‘Bergamo’ de AMD utilicen una plantilla de E/S con un puerto de aceleración, podría haber CPU Genoa-AI y Bergamo-AI con un acelerador ML.

También vale la pena señalar que AMD está buscando una potencia de diseño térmico configurable (cTDP) de 600 W para el procesador EPYC ‘Turin’ de quinta generación, que es el doble que el cTDP de la generación actual de procesadores EPYC 7003 series ‘Milan’. Además, la plataforma SP5 de AMD para CPU EPYC de 4.ª y 5.ª generación proporciona hasta 700 W de potencia durante periodos de tiempo muy cortos a los procesadores.

No sabemos cuánta energía necesitarán los futuros procesadores AMD 96 – 128 (Génova y Bérgamo), pero agregar un acelerador ML al paquete del procesador definitivamente aumentará el consumo. Con ese fin, tiene sentido asegurarse de que las plataformas de servidores de próxima generación puedan admitir CPU con aceleradores apilados.

Cree los mejores SoC para centros de datos

AMD ha estado hablando de unidades de procesamiento aceleradas (APU) para centros de datos desde que adquirió ATI Technologies en 2006. En los últimos 15 años, hemos escuchado acerca de varios proyectos de APU para centros de datos que integran núcleos x86 de propósito general para cargas de trabajo típicas y Radeon GPU para paralelismo Significativamente la carga de trabajo.

Ninguno de estos proyectos se materializó nunca, y hay muchas razones detrás de esto. Hasta cierto punto, dado que los núcleos bulldozer de AMD no eran competitivos, no tenía sentido construir un chip grande y costoso que pudiera tener una demanda tan limitada. Otra razón es que las GPU Radeon tradicionales no son compatibles con todos los formatos de datos e instrucciones necesarios para las cargas de trabajo del centro de datos/AI/ML/HPC, y que la primera GPU basada en CDNA de AMD solo apareció en 2020.

Pero ahora que AMD tiene una microarquitectura x86 competitiva, una arquitectura de GPU orientada a la computación, un conjunto de FPGA de Xilinx y una familia de procesadores programables de Pensando, puede que no tenga sentido poner estos diversos bloques de IP en un gran chip. Todo lo contrario, con las tecnologías de empaquetado actuales que ofrece TSMC y la tecnología de subprocesamiento Infinity Fabric de AMD, tiene mucho sentido construir módulos de mosaicos múltiples (o chips múltiples) con chips de procesador x86 de uso general, troqueles tipo E/S así como aceleradores GPU o FPGA.

De hecho, tiene más sentido crear un procesador de centro de datos de varios chips en lugar de una CPU grande y monolítica con varias direcciones IP integradas. Por ejemplo, una APU de centro de datos de varios niveles puede beneficiarse de mosaicos de CPU creados con el nodo N4X de rendimiento optimizado de TSMC, así como con una GPU o FPGA producida con tecnología de proceso N3E de densidad optimizada.

puerto acelerador universal

Otra parte importante de la patente no es una implementación específica diseñada para acelerar las cargas de trabajo de aprendizaje automático utilizando una FPGA o una GPU para el cálculo, sino el principio de agregar un acelerador de propósito especial a cualquier CPU. El puerto del acelerador será una interfaz universal provista en las plantillas de E/S de AMD, por lo que eventualmente, AMD podría agregar otros tipos de aceleradores a sus procesadores destinados a aplicaciones de clientes o centros de datos.

La descripción de la patente dice: «Debe entenderse que son posibles muchas variaciones en función de la divulgación del presente documento». Los procesadores adecuados incluyen, por ejemplo, un procesador de propósito general, un procesador de propósito especial, un procesador convencional, un procesador de gráficos, un procesador de aprendizaje automático, [a DSP, an ASIC, an FPGA]y otros tipos de circuitos integrados (IC). […] Estos procesadores se pueden fabricar configurando un proceso de fabricación utilizando los resultados de las instrucciones del lenguaje de descripción de hardware de procesamiento (HDL) y otros datos intermedios, incluidas las listas de red (tales instrucciones que se pueden almacenar en medios legibles por computadora). »

Si bien los FPGA, GPU y DSP se pueden usar para una variedad de aplicaciones incluso hoy en día, cosas como las unidades de procesamiento de datos (DPU) para centros de datos solo ganarán importancia en los próximos años. Las DPU son básicamente una de las aplicaciones emergentes que ahora tiene AMD. Pero a medida que el centro de datos cambia para procesar más tipos de datos y más rápido (y también lo hacen las computadoras cliente, como Apple integra la aceleración específica de la aplicación, como ProRes RAW, en sus SoC cliente), los aceleradores se vuelven cada vez más comunes. Esto significa que debe haber una forma de agregarlo a cualquier procesador de servidor o casi a cualquier otro procesador. De hecho, el puerto del acelerador de AMD es una forma relativamente sencilla de hacer esto.